Chapter 8

# **Multichannel Buffered Serial Port**

This chapter describes the operation and hardware of the two multichannel buffered serial ports (McBSP). This chapter also includes register definitions, and timing diagrams for the McBSPs.

## Topic

#### Page

| 8.1 | Features                                                                         |

|-----|----------------------------------------------------------------------------------|

| 8.2 | McBSP Interface Signals and Registers                                            |

| 8.3 | Data Transmission and Reception                                                  |

| 8.4 | $\mu\text{-LAW/A-LAW}$ Companding Hardware Operation $\hfill \ldots \hfill 8-46$ |

| 8.5 | Programmable Clock and Framing 8-49                                              |

| 8.6 | Multichannel Selection Operation                                                 |

| 8.7 | SPI Protocol: CLKSTP                                                             |

| 8.8 | McBSP Pins as General-Purpose I/O 8-79                                           |

|     |                                                                                  |

#### 8.1 Features

The multichannel buffered serial port (McBSP) is based on the standard serial port interface found on the TMS320C2x, 'C2xx, 'C5x, and 'C54x devices. The McBSP provides:

- Full-duplex communication

- Double-buffered data registers, which allow a continuous data stream

- Independent framing and clocking for receive and transmit

- Direct interface to industry-standard codecs, analog interface chips (AICs), and other serially connected A/D and D/A devices

- External shift clock or an internal, programmable frequency shift clock for data transfer

- Autobuffering capability through the five channel DMA controller.

In addition, the McBSP has the following capabilities:

- Direct interface to:

- T1/E1 framers

- MVIP switching compatible and ST-BUS compliant devices including:

- MVIP framers

- H.100 framers

- SCSA framers

- IOM-2 compliant devices

- AC97 compliant devices. The necessary multi-phase frame synchronization capability is provided

- IIS compliant devices

- SPI<sup>™</sup> devices

- Multichannel transmit and receive of up to 128 channels

- A wide selection of data sizes including 8, 12, 16, 20, 24, and 32 bits

- μ-Law and A-Law companding

- 8-bit data transfers with option of LSB or MSB first

- Programmable polarity for both frame synchronization and data clocks

- Highly programmable internal clock and frame generation

#### 8.2 McBSP Interface Signals and Registers

The multichannel buffered serial port (McBSP) consists of a data path and control path, which connect to external devices. Data is communicated to these external devices via separate pins for transmission and reception. Control information (clocking and frame synchronization) is communicated via four other pins. The device communicates to the McBSP via 32-bit wide control registers accessible via the internal peripheral bus.

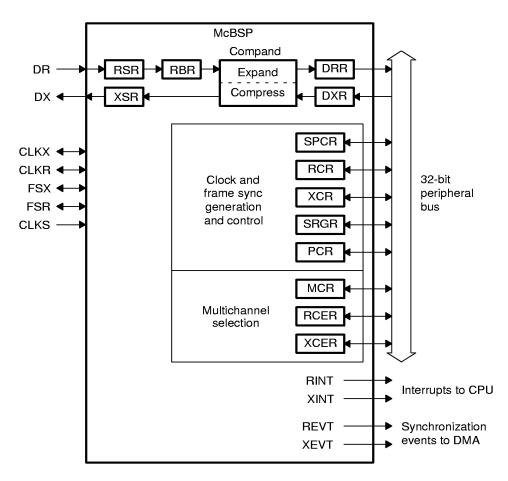

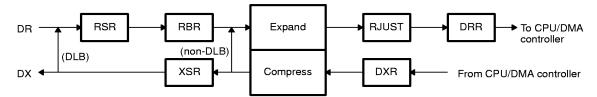

The McBSP consists of a data path and control path as shown in Figure 8–1. Seven pins listed in Table 8–1 connect the control and data paths to external devices.

#### Figure 8–1. McBSP Block Diagram

Data is communicated to devices interfacing to the McBSP via the data transmit (DX) pin for transmission and the data receive (DR) pin for reception. Control information (clocking and frame synchronization) is communicated via CLKX, CLKR, FSX, and FSR. The 'C6x communicates to the McBSP via 32-bit-wide control registers accessible via the internal peripheral bus (see section 3.4 *Peripheral Bus*). Either the CPU or the DMA controller reads the received data from the data receive register (DRR) and writes the data to be transmitted to the data transmit register (DXR). Data written to the DXR is shifted out to DX via the transmit shift register (XSR). Similarly, receive data on the DR pin is shifted into the receive shift register (RSR) and copied into the receive buffer register (RBR). RBR is then copied to DRR, which can be read by the CPU or the DMA controller. This allows internal data movement and external data communica-tions simultaneously.

The remaining registers accessible to the CPU configure the control mechanism of the McBSP. The McBSP registers are listed in Table 8–2. The control block consists of internal clock generation, frame-synchronization signal generation and control of these signals, and multichannel selection. This control block sends notification of important interrupts to the CPU and events to the DMA controller via the four signals shown in Table 8–3.

| Pin  | I/O/Z | Description                    |

|------|-------|--------------------------------|

| CLKR | I/O/Z | Receive clock                  |

| CLKX | I/O/Z | Transmit clock                 |

| CLKS | I     | External clock                 |

| DR   | I     | Received serial data           |

| DX   | O/Z   | Transmitted serial data        |

| FSR  | I/O/Z | Receive frame synchronization  |

| FSX  | I/O/Z | Transmit frame synchronization |

Table 8–1. McBSP Interface Signals

| Hex Byte  | e Address |              |                                  |         |  |

|-----------|-----------|--------------|----------------------------------|---------|--|

| McBSP 0   | McBSP 1   | Abbreviation | McBSP Register Name <sup>†</sup> | Section |  |

| -         | _         | RBR          | Receive buffer register          | 8.2     |  |

| -         | -         | RSR          | Receive shift register           | 8.2     |  |

| -         | -         | XSR          | Transmit shift register          | 8.2     |  |

| 018C 0000 | 0190 0000 | DRR          | Data receive register‡           | 8.2     |  |

| 018C 0004 | 0190 0004 | DXR          | Data transmit tegister           | 8.2     |  |

| 018C 0008 | 0190 0008 | SPCR         | Serial port control register     | 8.2.1   |  |

| 018C 000C | 0190 000C | RCR          | Receive control register         | 8.2.2   |  |

| 018C 0010 | 0190 0010 | XCR          | Transmit control register        | 8.2.2   |  |

| 018C 0014 | 0190 0014 | SRGR         | Sample rate generator register   | 8.5.1.1 |  |

| 018C 0018 | 0190 0018 | MCR          | Multichannel control register    | 8.6.1   |  |

| 018C 001C | 0190 001C | RCER         | Receive channel enable register  | 8.6.3.1 |  |

| 018C 0020 | 0190 0020 | XCER         | Transmit channel enable register | 8.6.3.1 |  |

| 018C 0024 | 0190 0024 | PCR          | Pin control register             | 8.2.1   |  |

#### Table 8–2. McBSP Registers

$^\dagger$  The RBR, RSR, and XSR are not directly accessible via the CPU or the DMA controller.  $^\ddagger$  The CPU and DMA controller can only read this register.

## Table 8–3. McBSP CPU Interrupts and DMA Synchronization Events

| Interrupt Name | Description                                          | Section |

|----------------|------------------------------------------------------|---------|

| RINT           | Receive Interrupt to CPU                             | 8.3.3   |

| XINT           | Transmit Interrupt to CPU                            | 8.3.3   |

| REVT           | Receive synchronization event to the DMA controller  | 8.3.2.1 |

| XEVT           | Transmit synchronization event to the DMA controller | 8.3.2.2 |

#### 8.2.1 Serial Port Configuration

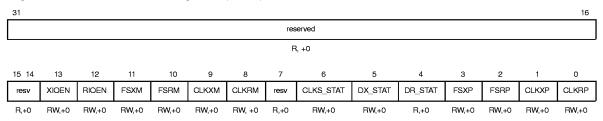

The serial port is configured via the 32-bit serial port control register (SPCR) and the pin control register (PCR) shown in Figure 8–2 and Figure 8–3. The SPCR and PCR contain McBSP status control bits. Table 8–4 and Table 8–5 summarize the description of the SPCR and the PCR fields, respectively.

The PCR is also used to configure the serial port pins as general purpose inputs or outputs during receiver and/or transmitter reset. This is described in Section 8.8.

| 31                             |        |        | 24     | 23        | 22  | 21  | 20        | 19                    | 18    | 17     | 16     |

|--------------------------------|--------|--------|--------|-----------|-----|-----|-----------|-----------------------|-------|--------|--------|

| reserved <sup>†</sup><br>R, +0 |        |        | FRST   | GRST      | XIN | ТМ  | XSYNCERR‡ | XEMPTY                | XRDY  | XRST   |        |

|                                |        |        | RW, +0 | RW, +0    | RW, | +0  | RW, +0    | R, +0                 | R, +0 | RW, +0 |        |

| 15                             | 14 13  | 12 11  | 10     |           | E   | 5 5 | 4         | 3                     | 2     | 1      | 0      |

| DLB                            | RJUST  | CLKSTP |        | reserved† |     | RIN | ТМ        | RSYNCERR <sup>‡</sup> | RFULL | RRDY   | RRST   |

| RW,+0                          | RW, +0 | RW,+0  |        | R, +0     |     | RW, | +0        | RW, +0                | R, +0 | R, +0  | RW, +0 |

<sup>†</sup>Reserved-fields have *no* storage associated with them. However, they are always read as 0.

+ Writing a 1 to this bit will set the error condition. Thus, it is used mainly for testing purposes or if this operation is desired.

| Name     | Function                                                                                                                                  | Section |  |  |  |  |  |  |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------|---------|--|--|--|--|--|--|

| FRST     | Frame sync generator reset                                                                                                                | 8.5.3   |  |  |  |  |  |  |

|          | FRST = 0: The frame sync generation logic is reset. Frame sync signal is not generated by the sample rate generator.                      |         |  |  |  |  |  |  |

|          | FRST = 1: Frame sync signal is generated after eight CLKG clocks. All frame counters are loaded with their programmed values.             |         |  |  |  |  |  |  |

| GRST     | sample rate generator reset                                                                                                               | 8.5.1.2 |  |  |  |  |  |  |

|          | $\overline{\text{GRST}}$ = 0: Sample rate generator is reset.                                                                             |         |  |  |  |  |  |  |

|          | GRST = 1: Sample rate generator is pulled out of reset; CLKG is driven as per programmed values in sample rate generator register (SRGR). |         |  |  |  |  |  |  |

| RINTM    | Receive interrupt mode                                                                                                                    | 8.3.3   |  |  |  |  |  |  |

|          | RINTM = 00b: RINT driven by RRDY                                                                                                          |         |  |  |  |  |  |  |

|          | RINTM = 01b: RINT generated by end-of-subframe in multichannel operation                                                                  |         |  |  |  |  |  |  |

|          | RINTM = 10b: RINT generated by a new frame synchronization                                                                                |         |  |  |  |  |  |  |

|          | RINTM = 11b: RINT generated by RSYNCERR                                                                                                   |         |  |  |  |  |  |  |

| XINTM    | Transmit interrupt mode                                                                                                                   |         |  |  |  |  |  |  |

|          | XINTM = 00b: XINT driven by XRDY                                                                                                          |         |  |  |  |  |  |  |

|          | XINTM = 01b: XINT generated by end-of-subframe or in multichannel<br>operation                                                            |         |  |  |  |  |  |  |

|          | XINTM = 10b: XINT generated by a new frame synchronization                                                                                |         |  |  |  |  |  |  |

|          | XINTM = 11b: XINT generated by XSYNCERR                                                                                                   |         |  |  |  |  |  |  |

| RSYNCERR | Receive synchronization error                                                                                                             | 8.3.7.2 |  |  |  |  |  |  |

|          | RSYNCERR = 0: no frame synchronization error                                                                                              | 8.3.7.5 |  |  |  |  |  |  |

|          | RSYNCERR = 1: frame synchronization error detected by McBSP.                                                                              |         |  |  |  |  |  |  |

| XSYNCERR | Transmit synchronization error                                                                                                            | 8.3.7.2 |  |  |  |  |  |  |

|          | XSYNCERR = 0: no frame synchronization error                                                                                              | 8.3.7.5 |  |  |  |  |  |  |

|          | XSYNCERR = 1: frame synchronization error detected by McBSP.                                                                              |         |  |  |  |  |  |  |

| XEMPTY   | Transmit shift register (XSR) empty                                                                                                       | 8.3.7.4 |  |  |  |  |  |  |

|          | XEMPTY = 0: XSR is empty                                                                                                                  |         |  |  |  |  |  |  |

|          | XEMPTY = 1: XSR is not empty                                                                                                              |         |  |  |  |  |  |  |

| RFULL    | Receive shift register (RSR) Full error condition                                                                                         | 8.3.7.1 |  |  |  |  |  |  |

|          | RFULL = 0: Receiver is not in overrun condition.                                                                                          |         |  |  |  |  |  |  |

|          | RFULL = 1: DRR is not read, RBR is full, and RSR is full with a new element.                                                              |         |  |  |  |  |  |  |

Table 8–4. Serial Port Control Register (SPCR) Field Descriptions

| Name | Function                                                                                  | Section            |

|------|-------------------------------------------------------------------------------------------|--------------------|

| RRDY | Receiver ready                                                                            | 8.3.2              |

|      | RRDY = 0: Receiver/transmitter is not ready.                                              |                    |

|      | RRDY = 1: Receiver is ready with data to be read from DRR.                                |                    |

| XRDY | Transmitter ready                                                                         | 8.3.2              |

|      | XRDY = 0: The transmitter is not ready.                                                   |                    |

|      | XRDY = 1: The transmitter is ready for data to be written to DXR.                         |                    |

| RRST | Receiver reset. This resets or enables the receiver.                                      | 8.3.1              |

|      | $\overline{\text{RRST}}$ = 0: The serial port receiver is disabled and is in reset state. |                    |

|      | $\overrightarrow{RRST}$ = 1: The serial port receiver is enabled.                         |                    |

| XRST | Transmitter reset. This resets or enables the transmitter.                                | 8.3.1              |

|      | $\overline{\text{XRST}}$ = 0: The serial port transmitter is disabled and in reset state. |                    |

|      | $\overline{\text{XRST}}$ = 1: The serial port transmitter is enabled.                     |                    |

| DLB  | Digital loop back mode                                                                    | 8.5.2.5            |

|      | DLB = 0: digital loop back mode disabled                                                  | 8.5.2.6<br>8.5.3.2 |

|      | DLB = 1: digital loop back mode enabled                                                   | 0.0.0.2            |

Table 8–4. Serial Port Control Register (SPCR) Field Descriptions (Continued)

| Name   | Function                                                                              | Section |  |  |  |  |  |  |  |

|--------|---------------------------------------------------------------------------------------|---------|--|--|--|--|--|--|--|

| RJUST  | Receive data sign-extension and justification mode                                    |         |  |  |  |  |  |  |  |

|        | RJUST = 00b: right-justify and zero-fill MSBs in DRR                                  |         |  |  |  |  |  |  |  |

|        | RJUST = 01b: right-justify and sign-extend MSBs in DRR                                |         |  |  |  |  |  |  |  |

|        | RJUST = 10b: left-justify and zero-fill LSBs in DRR                                   |         |  |  |  |  |  |  |  |

|        | RJUST = 11b: reserved                                                                 |         |  |  |  |  |  |  |  |

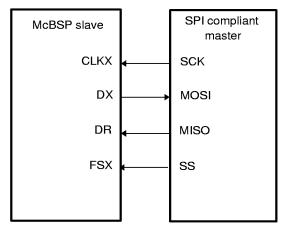

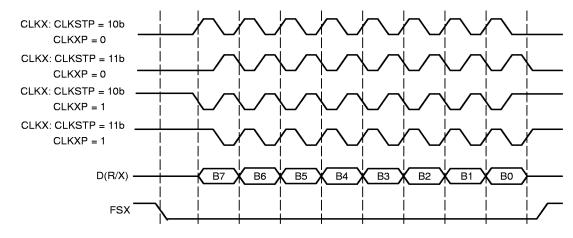

| CLKSTP | Clock stop mode                                                                       |         |  |  |  |  |  |  |  |

|        | CLKSTP = 0Xb: Clock stop mode disabled. Normal clocking enabled for non-<br>SPI mode. |         |  |  |  |  |  |  |  |

|        | Clock stop mode enabled for various SPI™ modes when:                                  |         |  |  |  |  |  |  |  |

|        | CLKSTP = 10b and CLKXP = 0: Clock starts with rising edge without delay               |         |  |  |  |  |  |  |  |

|        | CLKSTP = 10b and CLKXP = 1: Clock starts with falling edge without delay              |         |  |  |  |  |  |  |  |

|        | CLKSTP = 11b and CLKXP = 0: Clock starts with rising edge with delay                  |         |  |  |  |  |  |  |  |

|        | CLKSTP = 11b and CLKXP = 1: Clock starts with falling edge with delay                 |         |  |  |  |  |  |  |  |

Table 8–4. Serial Port Control Register (SPCR) Field Descriptions (Continued)

Figure 8–3. Pin Control Register (PCR)

| Name  | Function                                                                                                                                                                                     | Section    |  |  |  |  |  |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|--|--|--|--|--|

| RIOEN | Receiver in general-purpose I/O mode ONLY when $\overrightarrow{\text{RRST}} = 0$ in SPCR                                                                                                    | 8.8        |  |  |  |  |  |

|       | RIOEN = 0: DR and CLKS pins are not general-purpose inputs; FSR, CLKR are not general-purpose I/Os.                                                                                          |            |  |  |  |  |  |

|       | RIOEN = 1: DR and CLKS pins are general-purpose inputs. FSR, CLKR are general-purpose I/Os. These serial port pins do not perform serial port operation.                                     |            |  |  |  |  |  |

| XIOEN | Transmitter in general-purpose I/O mode ONLY when $\overline{\text{XRST}} = 0$ in SPCR                                                                                                       | 8.8        |  |  |  |  |  |

|       | XIOEN = 0: CLKS pin is not a general-purpose input; DX pin is not a general<br>purpose output; FSX, CLKX are not general-purpose I/Os.                                                       |            |  |  |  |  |  |

|       | XIOEN = 1: CLKS pin is a general-purpose input; DX pin is a general-purpose out-<br>put. FSX, CLKX are general-purpose I/Os. These serial port pins do<br>not perform serial port operation. |            |  |  |  |  |  |

| FSXM  | Transmit frame synchronization mode                                                                                                                                                          | 8.5.3.3    |  |  |  |  |  |

|       | FSXM = 0: Frame synchronization signal is provided by an external source.<br>FSX is an input pin.                                                                                            |            |  |  |  |  |  |

|       | FSXM = 1: Frame synchronization generation is determined by the Sample<br>Rate Generator frame synchronization mode bit FSGM in the<br>SRGR.                                                 |            |  |  |  |  |  |

| FSRM  | Receive frame synchronization mode                                                                                                                                                           | 8.5.3.2    |  |  |  |  |  |

|       | FSRM = 0: Frame synchronization signals are generated by an external de-<br>vice. FSR is an input pin.                                                                                       | and<br>8.8 |  |  |  |  |  |

|       | FSRM = 1: Frame synchronization signals are generated internally by sample rate generator. FSR is an output pin except when GSYNC = 1 (subsection 8.5.1.1) in SRGR.                          |            |  |  |  |  |  |

| CLKRM | Receiver clock mode                                                                                                                                                                          | 8.5.2.6    |  |  |  |  |  |

|       | Case 1: Digital loop back mode not set (DLB = 0) in SPCR                                                                                                                                     | and<br>8.8 |  |  |  |  |  |

|       | CLKRM = 0: Receive clock (CLKR) is an input driven by an external clock.                                                                                                                     |            |  |  |  |  |  |

|       | CLKRM = 1: CLKR is an output pin and is driven by the sample rate generator.                                                                                                                 |            |  |  |  |  |  |

|       | Case 2: Digital loop back mode set (DLB = 1) in SPCR                                                                                                                                         |            |  |  |  |  |  |

|       | CLKRM = 0: Receive clock (not the CLKR pin) is driven by the transmit clock<br>(CLKX) which is based on the CLKXM bit in PCR. CLKR is in<br>high-impedance.                                  |            |  |  |  |  |  |

|       | CLKRM = 1: CLKR is an output pin and is driven by the transmit clock. The<br>transmit clock is derived based on CLKXM bit in the PCR.                                                        |            |  |  |  |  |  |

Table 8–5. Pin Control Register (PCR) Field Descriptions

| Name                                             | Function                                                                                                                                                                         | Section    |  |  |  |  |  |  |

|--------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|--|--|--|--|--|--|

| CLKXM<br>CLKS_STAT<br>DX_STAT<br>DR_STAT<br>=SRP | Transmitter clock mode                                                                                                                                                           |            |  |  |  |  |  |  |

|                                                  | CLKXM = 0: Transmitter clock is driven by an external clock with CLKX as an input pin.                                                                                           | and<br>8.8 |  |  |  |  |  |  |

|                                                  | CLKXM = 1: CLKX is an output pin and is driven by the internal sample rate generator.                                                                                            |            |  |  |  |  |  |  |

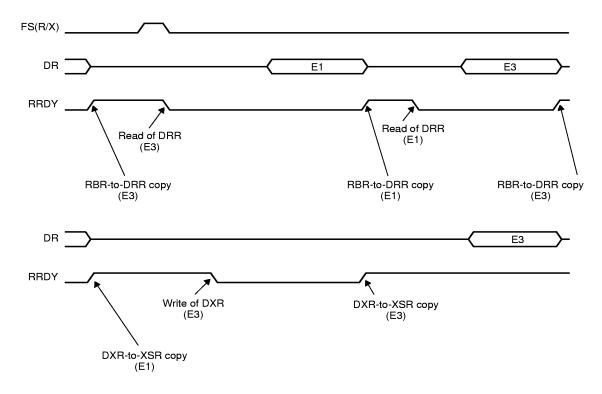

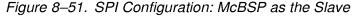

|                                                  | During SPI mode (CLKSTP in SPCR is a nonzero value):                                                                                                                             | 8.7        |  |  |  |  |  |  |

|                                                  | CLKXM = 0: McBSP is a slave and (CLKX) is driven by the SPI master in the<br>system. CLKR is internally driven by CLKX.                                                          |            |  |  |  |  |  |  |

|                                                  | CLKXM = 1: McBSP is a master and generates the transmitter clock (CLKX)<br>to drive its receiver clock (CLKR) and the shift clock of the SPI-<br>compliant slaves in the system. |            |  |  |  |  |  |  |

| CLKS_STAT                                        | CLKS pin status. Reflects value on CLKS pin when selected as a general purpose input.                                                                                            | 8.8        |  |  |  |  |  |  |

| DX_STAT                                          | DX pin status. Reflects value driven on to DX pin when selected as a general purpose output.                                                                                     | 8.8        |  |  |  |  |  |  |

| DR_STAT                                          | DR pin status. Reflects value on DR pin when selected as a general purpose input.                                                                                                | 8.8        |  |  |  |  |  |  |

| FSRP                                             | Receive frame synchronization polarity                                                                                                                                           | 8.3.4.1    |  |  |  |  |  |  |

|                                                  | FSRP = 0: Frame synchronization pulse FSR is active high                                                                                                                         | and<br>8.8 |  |  |  |  |  |  |

|                                                  | FSRP = 1: Frame synchronization pulse FSR is active low                                                                                                                          | 0.0        |  |  |  |  |  |  |

| FSXP                                             | Transmit frame synchronization polarity                                                                                                                                          | 8.3.4.1    |  |  |  |  |  |  |

|                                                  | FSXP = 0: Frame synchronization pulse FSX is active high                                                                                                                         | and        |  |  |  |  |  |  |

|                                                  | FSXP = 1: Frame synchronization pulse FSX is active low                                                                                                                          | 8.8        |  |  |  |  |  |  |

| CLKXP                                            | Transmit clock polarity                                                                                                                                                          | 8.3.4.1    |  |  |  |  |  |  |

|                                                  | CLKXP = 0: Transmit data driven on rising edge of CLKX                                                                                                                           | and        |  |  |  |  |  |  |

|                                                  | CLKXP = 1: Transmit data driven on falling edge of CLKX                                                                                                                          | 8.8        |  |  |  |  |  |  |

| CLKRP                                            | Receive clock polarity                                                                                                                                                           | 8.3.4.1    |  |  |  |  |  |  |

|                                                  | CLKRP = 0: Receive data sampled on falling edge of CLKR                                                                                                                          | and<br>8.8 |  |  |  |  |  |  |

|                                                  | CLKRP = 1: Receive data sampled on rising edge of CLKR                                                                                                                           | 0.0        |  |  |  |  |  |  |

Table 8–5. Pin Control Register (PCR) Field Descriptions (Continued)

#### 8.2.2 Receive and Transmit Control Registers: RCR and XCR

The receive and transmit control registers (RCR and XCR), shown in Figure 8–4 and Figure 8–5, configure various parameters of the receive and transmit operations respectively.

|              | 31       | 30      | 24 | 23 |         | 21 | 20     | 19 | 18       | 17      | 16 |

|--------------|----------|---------|----|----|---------|----|--------|----|----------|---------|----|

|              | RPHASE   | RFRLEN2 |    |    | RWDLEN2 |    | RCOMPA | ND | RFIG     | RDATDLY |    |

| -            | RW, +0   | RW, +0  |    |    | RW, +0  |    | RW, +0 | )  | RW, +0   | RW, +0  |    |

|              | 15       | 14      | 8  | 7  |         | 5  | 4      |    |          |         | 0  |

|              | reserved | RFRLEN1 |    |    | RWDLEN1 |    |        |    | reserved |         |    |

| R, +0 RW, +0 |          |         |    |    | RW, +0  |    |        |    | R, +0    |         |    |

| Figure 8–4. | Receive | Control | Reaister | (RCR) |

|-------------|---------|---------|----------|-------|

|             |         |         |          | 1     |

#### Figure 8–5. Transmit Control Register (XCR)

| <br>31     | 30      | 24 | 23 |         | 21 | 20  | 19    | 18      |    | 17      | 16 |

|------------|---------|----|----|---------|----|-----|-------|---------|----|---------|----|

| XPHASE     | XFRLEN2 |    |    | XWDLEN2 |    | хсо | MPAND | XFIG    |    | XDATDLY |    |

| <br>RW, +0 | RW, +0  |    |    | RW, +0  |    | RV  | V, +0 | RW, +0  |    | RW, +0  |    |

| 15         | 14      | 8  | 7  |         | 5  | 4   |       |         |    |         | 0  |

| reserved   | XFRLEN1 |    |    | XWDLEN1 |    |     |       | reserve | ed |         |    |

| <br>R, +0  | RW, +0  |    | -  | RW, +0  |    |     |       | R, +0   | )  |         |    |

| Name        | Function                                      | Section |

|-------------|-----------------------------------------------|---------|

| RPHASE      | Receive phases                                | 8.3.4.2 |

|             | RPHASE = 0: single phase frame                |         |

|             | RPHASE = 1: dual phase frame                  |         |

| XPHASE      | Transmit phases                               | 8.3.4.2 |

|             | XPHASE = 0: single phase frame                |         |

|             | XPHASE = 1: dual phase frame                  |         |

| RFRLEN(1/2) | Receive frame length in phase 1 and phase 2   | 8.3.4.3 |

|             | RFRLEN(1/2) = 000 0000b: 1 word per phase     |         |

|             | RFRLEN(1/2) = 000 0001b: 2 words per phase    |         |

|             | •                                             |         |

|             | •                                             |         |

|             | RFRLEN(1/2) = 111 1111b: 128 words per phase  |         |

| XFRLEN(1/2) | Transmit frame length in phase 1 and phase 2  | 8.3.4.3 |

|             | XFRLEN(1/2) = 000 0000b: 1 word per phase     |         |

|             | XFRLEN(1/2) = 000 0001b: 2 words per phase    |         |

|             | •                                             |         |

|             | XFRLEN(1/2) = 111 1111b: 128 words per phase  |         |

| RWDLEN(1/2) | Receive element length in phase 1 and phase 2 | 8.3.4.4 |

|             | RWDLEN(1/2) = 000b: 8 bits                    |         |

|             | RWDLEN(1/2) = 001b: 12 bits                   |         |

|             | RWDLEN(1/2) = 010b: 16 bits                   |         |

|             | RWDLEN(1/2) = 011b: 20 bits                   |         |

|             | RWDLEN(1/2) = 100b: 24 bits                   |         |

|             | RWDLEN(1/2) = 101b: 32 bits                   |         |

|             | RWDLEN(1/2) = 11Xb: reserved                  |         |

Table 8-6. Receive/Transmit Control Register (RCR/XCR) Field Description

| Name        | Function                                                                                                                       | Section |

|-------------|--------------------------------------------------------------------------------------------------------------------------------|---------|

| XWDLEN(1/2) | Transmit element length in phase 1 and phase 2                                                                                 | 8.3.4.4 |

|             | XWDLEN(1/2) = 000b: 8 bits                                                                                                     |         |

|             | XWDLEN(1/2) = 001b: 12 bits                                                                                                    |         |

|             | XWDLEN(1/2) = 010b: 16 bits                                                                                                    |         |

|             | XWDLEN(1/2) = 011b: 20 bits                                                                                                    |         |

|             | XWDLEN(1/2) = 100b: 24 bits                                                                                                    |         |

|             | XWDLEN(1/2) = 101b: 32 bits                                                                                                    |         |

|             | XWDLEN(1/2) = 11Xb: reserved                                                                                                   |         |

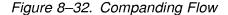

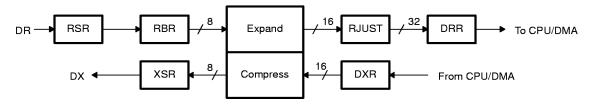

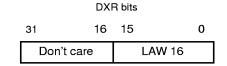

| RCOMPAND    | Receive companding mode. Modes other than 00b are only applicable when the appropriate RWDLEN is 000b, indicating 8-bit data.  | 8.4     |

|             | RCOMPAND = 00b: no companding, data transfer starts with MSB first.                                                            |         |

|             | RCOMPAND = 01b: no companding, 8-bit data, transfer starts with LSB first.                                                     |         |

|             | RCOMPAND = 10b: compand using $\mu$ -law for receive data.                                                                     |         |

|             | RCOMPAND = 11b: compand using A-law for receive data.                                                                          |         |

| XCOMPAND    | Transmit companding mode. Modes other than 00b are only applicable when the appropriate XWDLEN is 000b, indicating 8-bit data. | 8.4     |

|             | XCOMPAND = 00b: no companding, data transfer starts with MSB<br>first.                                                         |         |

|             | XCOMPAND = 01b: no companding, 8-bit data, transfer starts with LSB first.                                                     |         |

|             | XCOMPAND = 10b: compand using $\mu$ -law for transmit data.                                                                    |         |

|             | XCOMPAND = 11b: compand using A-law for transmit data.                                                                         |         |

| RFIG        | Receive frame ignore                                                                                                           | 8.3.6.1 |

|             | RFIG = 0: Unexpected receive frame synchronization pulses restart the transfer.                                                |         |

|             | RFIG = 1: Unexpected receive frame synchronization pulses are ig-<br>nored.                                                    |         |

| XFIG        | Transmit frame ignore                                                                                                          | 8.3.6.1 |

|             | XFIG = 0: Unexpected transmit frame synchronization pulses restart the transfer.                                               |         |

|             | XFIG = 1: Unexpected transmit frame synchronization pulses are<br>ignored.                                                     |         |

Table 8–6. Receive/Transmit Control Register (RCR/XCR) Field Description (Continued)

| Name    | Function                        | Section |

|---------|---------------------------------|---------|

| RDATDLY | Receive data delay              | 8.3.4.6 |

|         | RDATDLY = 00b: 0-bit data delay |         |

|         | RDATDLY = 01b: 1-bit data delay |         |

|         | RDATDLY = 10b: 2-bit data delay |         |

|         | RDATDLY = 11b: reserved         |         |

| XDATDLY | Transmit data delay             | 8.3.4.6 |

|         | XDATDLY = 00b: 0-bit data delay |         |

|         | XDATDLY = 01b: 1-bit data delay |         |

|         | XDATDLY = 10b: 2-bit data delay |         |

|         | XDATDLY = 11b: reserved         |         |

Table 8–6. Receive/Transmit Control Register (RCR/XCR) Field Description (Continued)

#### 8.3 Data Transmission and Reception

As shown in Figure 8–1, on page 8-3 the receive operation is triple buffered and transmit operation is double buffered. Receive data arrives on DR and is shifted into the RSR. Once a full element (8, 12, 16, 20, 24, or 32 bits) is received, the RSR is copied to the receive buffer register (RBR) only if RBR is not full. RBR is then copied to DRR unless DRR has not been read by the CPU or the DMA controller.

Transmit data is written by the CPU or the DMA controller to the DXR. If there is no data in the XSR, the value in the DXR is copied to the XSR. Otherwise, the DXR is copied to the XSR when the last bit of data is shifted out on DX. After transmit frame synchronization, the XSR begins shifting out the transmit data on DX.

#### 8.3.1 Resetting the Serial Port: (R/X)RST, GRST, and RESET

The serial port can be reset in the following two ways:

- □ Device reset (RESET pin is low) places the receiver, the transmitter and the sample rate generator in reset. When the device reset is removed (RESET = 1), FRST = GRST = RRST = XRST = 0, keeping the entire serial port in the reset state.

- □ The serial port transmitter and receiver can be independently reset by the XRST and RRST bits in the SPCR. The sample rate generator is reset by the GRST bit in the SPCR.

Table 8–7 shows the state of the McBSP pins when the serial port is reset by each of these methods.

| McBSP |           | Device Reset    |                                                                       |

|-------|-----------|-----------------|-----------------------------------------------------------------------|

| Pins  | Direction | (RESET = 0)     | McBSP Reset                                                           |

|       |           |                 | Receiver Reset ( $\overline{RRST} = 0$ and $\overline{GRST} = 1$ )    |

| DR    | I         | Input           | Input                                                                 |

| CLKR  | I/O/Z     | Input           | Known state if input; CLKR if output                                  |

| FSR   | I/O/Z     | Input           | Known state if input; FSRP(inactive state) if output                  |

| CLKS  | I         | Input           | Input                                                                 |

|       |           |                 | Transmitter Reset ( $\overline{XRST} = 0$ and $\overline{GRST} = 1$ ) |

| DX    | 0         | High impedance† | High impedance                                                        |

| CLKX  | I/O/Z     | Input           | Known state if input; CLKX if output                                  |

| FSX   | I/O/Z     | Input           | Known state if input; FSXP(inactive state) if output                  |

| CLKS  | I         | Input           | Input                                                                 |

#### Table 8–7. Reset State of McBSP Pins

- Device reset or McBSP reset: When the McBSP is reset in either of these two ways, the state machine is reset to its initial state. This initial state includes resetting all counters and status bits. The receive status bits include RFULL, RRDY, and RSYNCERR. The transmit status bits are XEMPTY, XRDY, and XSYNCERR.

- Device reset: When McBSP is reset due to device reset, the entire serial port (including the transmitter, receiver, and the sample rate generator) is reset. All input-only pins and 3-state pins should be in a known state. The output-only pin, DX, is in the high impedance state. Since the sample rate generator is also reset (GRST = 0), the sample rate generator clock, CLKG, is driven by a divide-by-2 CPU clock, and the frame sync signal, FSG, is not generated. See subsection 8.5.1.2 for more information on sample rate generator reset. When the device is pulled out of reset, the serial port remains in the reset condition ((R/X)RST = FRST = 0), and in this condition the serial port pins can be used as general-purpose I/O as described in section 8.8.

- **McBSP reset:** When the receiver and transmitter reset bits, RRST and XRST, are written with 0, the respective portions of the McBSP are reset, and activity in the corresponding section stops. All input-only pins, such as DR and CLKS, and all other pins that are configured as inputs are in a known state. FS(R/X) is driven to its inactive state (same as its polarity bit, FS(R/X)P if it is an output. If CLK(R/X) are programmed as outputs, they are driven by CLKG, provided that GRST = 1. Lastly, the DX pin will be in the high-impedance state when the transmitter is reset. During normal operation, the sample rate generator can be reset by writing a 0 to GRST. GRST should be low only when neither the transmitter nor the receiver is using the sample rate generator. In this case, the internal sample rate generator clock CLKG, and its frame sync signal (FSG) is driven inactive (low). When the sample rate generator is not in the reset state ( $\overline{GRST} = 1$ ), FSR and FSX are in an inactive state when  $\overline{RRST} = 0$  and  $\overline{XRST} = 0$ , respectively, even if they are outputs driven by FSG. This ensures that when only one portion of the McBSP is in reset, the other portion can continue operation when  $\overline{\text{FRST}} = 1$  and frame sync is driven by FSG.

- Sample rate generator reset: As mentioned previously, the sample rate generator is reset when the device is reset or when its reset bit, GRST, is written with 0. In the case of device reset, the CLKG signal is driven by a divide-by-2 CPU clock and FSG is driven inactive (low). If you want to reset the sample rate generator when neither the transmitter nor receiver is fed by the CLKG and FSG, GRST in the SRGR can be programmed to 0. Here, CLKG and FSG are driven inactive (low). When GRST = 1, CLKG comes up running as programmed in the SRGR. Later if FRST = 1, FSG is driven active (high) after eight cycles have elapsed.

The serial port initialization procedure is as follows:

- Set XRST = RRST = FRST = 0 in SPCR. If the device is coming out of reset, this step is not required.

- 2) Program only the McBSP configuration registers (and not the data registers) listed in Table 8–2 as required when the serial port is in the reset state  $(\overline{XRST} = \overline{RRST} = \overline{FRST} = 0)$ .

- 3) Wait two bit clocks. This is to ensure proper synchronization internally.

- 4) Set up data acquisition as desired.

- 5) Set  $\overline{\text{XRST}} = \overline{\text{RRST}} = 1$  to enable the serial port. The value written to the SPCR at this time should have only the reset bits changed to 1 and the remaining bit-fields should have the same value as in Step 2 above.

- Set FRST = 1. Now the McBSP is ready to transmit and/or receive, if it is the frame master.

Alternatively, on either write (steps 1 and 5 above), the transmitter and receiver can be placed in or taken out of reset individually by modifying only the desired bit. The necessary duration of the active(low) period of  $\overline{XRST}$  or  $\overline{RRST}$  is at least two bit clocks (CLKR/CLKX). This procedure for reset initialization can be applied generally when the receiver or transmitter has to be reset during its normal operation and also when the sample rate generator is not used for either operation. The sample rate generator reset procedure is explained in section 8.5.1.2.

#### Notes:

- The appropriate-fields in the serial port configuration registers SPCR, PCR, RCR, XCR, and SRGR should only be modified when the affected portion of the serial port is in reset.

- 2) The data transmit register, DXR, should be loaded by the CPU or DMA only when the transmitter is not in reset (XRST = 1). The exception to this rule is during non-digital loop back mode, which is described in section 8.4.1.

- 3) The multichannel selection registers MCR, XCER, and RCER can be modified at any time as long as they are not being used by the current block in the multichannel selection. See section 8.6.3.2 for further information.

#### 8.3.2 Determining Ready Status

RRDY and XRDY indicate the ready state of the McBSP receiver and transmitter, respectively. Writes and reads of the serial port can be synchronized by polling RRDY and XRDY, or by using the events sent to the DMA controller (REVT and XEVT) or the interrupts to the CPU (RINT and XINT) that the events generate. Note that reading the DRR and writing to DXR affects RRDY and XRDY, respectively.

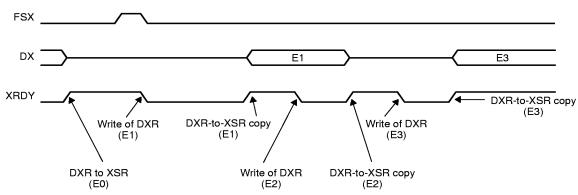

#### 8.3.2.1 Receive Ready Status: REVT, RINT, and RRDY

RRDY = 1 indicates that the RBR contents have been copied to the DRR and that the data can be read by either the CPU or the DMA controller. Once that data has been read by either the CPU or the DMA controller, RRDY is cleared to 0. Also, at device reset or serial port receiver reset ( $\overline{RRST} = 0$ ), the RRDY is cleared to 0 to indicate no data has yet been received and loaded into DRR. RRDY directly drives the McBSP receive event to the DMA controller (via REVT). Also, the McBSP receive interrupt (RINT) to the CPU can be driven by RRDY if RINTM = 00b (default value) in the SPCR.

#### 8.3.2.2 Transmit Ready Status: XEVT, XINT, and XRDY

XRDY = 1 indicates that the DXR contents have been copied to XSR and that DXR is ready to be loaded with a new data word. When the transmitter transitions from reset to nonreset ( $\overline{XRST}$  transitions from 0 to 1), XRDY also transitions from 0 to 1 indicating that the DXR is ready for new data. Once new data is loaded by the CPU or the DMA controller, XRDY is cleared to 0. However, once this data is copied from the DXR to the XSR, XRDY transitions again from 0 to 1. The CPU or the DMA controller can write to DXR although XSR has not yet been shifted out on DX. XRDY directly drives the transmit interrupt (XINT) to the CPU can be driven by XRDY if XINTM = 00b (default value) in the SPCR.

#### 8.3.3 CPU Interrupts: (R/X)INT

The receive interrupt (RINT) and transmit interrupt (XINT) signal the CPU of changes to the serial port status. Four options exist for configuring these interrupts. These options are set by the receive/transmit interrupt mode field, (R/X)INTM, in the SPCR. The possible values of the mode and the configurations they represent are:

- $\square (R/X)INTM = 00b.$  Interrupt on every serial element by tracking the (R/X)RDY bits in the SPCR.

- $\square$  (R/X)INTM = 01b. Interrupt at the end of a subframe (16 elements or less) within a frame. See subsection 8.6.3.3 for details.

- (R/X)INTM = 10b. Interrupt on detection of frame synchronization pulses. This generates an interrupt even when the transmitter/receiver is in reset. This is done by synchronizing the incoming frame sync pulse to the CPU clock and sending it to the CPU via (R/X)INT. This is described in subsection 8.5.3.4.

- (R/X)INTM = 11b. Interrupt on frame synchronization error. Note that if any of the other interrupt modes are selected, (R/X)SYNCERR may be read when servicing the interrupts to detect this condition. See subsections 8.3.7.2 and 8.3.7.5 for more details on synchronization error.

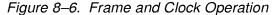

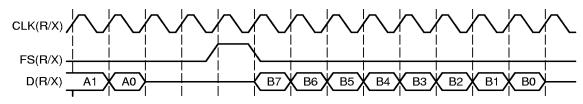

#### 8.3.4 Frame and Clock Configuration

Figure 8–6 shows typical operation of the McBSP clock and frame sync signals. Serial clocks CLKR and CLKX define the boundaries between bits for receive and transmit respectively. Similarly, frame sync signals FSR and FSX define the beginning of an element transfer. The McBSP allows configuration of various parameters for data frame synchronization. This can be done independently for receive and transmit and consists of the following items:

- Polarities of FSR, FSX, CLKX, and CLKR

- A choice of single- or dual-phase frames

- For each phase, the number of elements per frame

- For each phase, the number of bits per element

- Subsequent frame synchronization can restart the serial data stream or be ignored.

- The data delay from frame synchronization to first data bit can be 0-, 1-, or 2-bit delays.

- Right- or left-justification as well as sign-extension or zero-filling can be chosen for receive data.

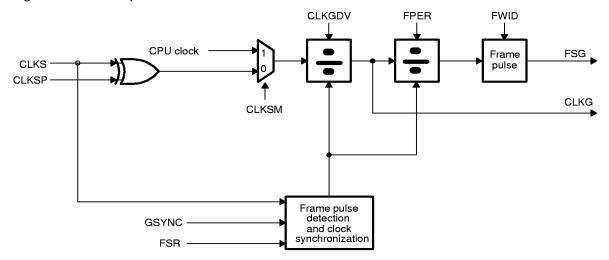

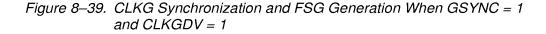

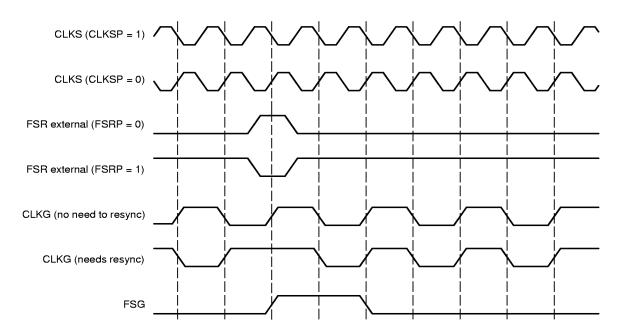

#### 8.3.4.1 Frame and Clock Operation

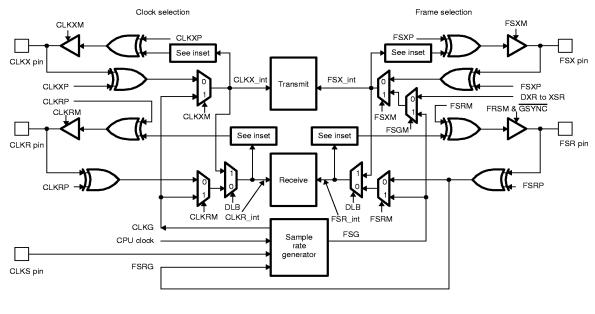

Receive and transmit frame sync pulses can be generated either internally by the sample rate generator (see section 8.5.1) or driven by an external input. The source of frame sync is selected by programming the mode bit, FS(R/X)M, in the PCR. FSR is also affected by the GSYNC bit in the SRGR (see section 8.5.3.2 for details). Similarly, receive and transmit clocks can be selected to be inputs or outputs by programming the mode bit, CLK(R/X)M, in the PCR.

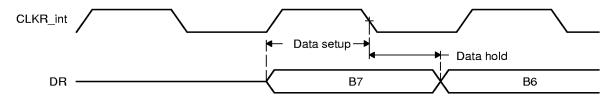

When FSR and FSX are inputs (FSXM = FSRM = 0), the McBSP detects them on the internal falling edge of clock, CLKR\_int and CLKX\_int, respectively (see Figure 8–36 on page 8-49). The receive data arriving at DR pin is also sampled

on the falling edge of CLKR\_int. These internal clock signals are either derived from external source via CLK(R/X) pins or driven by the sample rate generator clock (CLKG) internal to the McBSP.

When FSR and FSX are outputs driven by the sample rate generator, they are generated (transition to their active state) on the rising edge of the internal clock, CLK(R/X)\_int. Similarly, data on DX is output on the rising edge of CLKX\_int. See section 8.3.4.6 for further details.

FSRP, FSXP, CLKRP, and CLKXP configure the polarities of FSR, FSX, CLKR, and CLKX as shown in Table 8–5. All frame sync signals (FSR\_int and FSX\_int) internal to the serial port are active high. If the serial port is configured for external frame synchronization (FSR/FSX are inputs to the McBSP), and FSRP = FSXP = 1, the external active low frame sync signals are inverted before being sent to the receiver signal (FSR\_int) and transmitter signal (FSX\_int). Similarly, if internal synchronization is selected (FSR/FSX are outputs and GSYNC = 0), the internal active-high sync signals are inverted if the polarity bit FS(R/X)P = 1, before being sent to the FS(R/X) pin. Figure 8–36 shows this inversion using XOR gates.

On the transmit side, the transmit clock polarity bit, CLKXP, sets the edge used to shift and clock out transmit data. Data is always transmitted on the rising edge of CLKX\_int. If CLKXP = 1 and external clocking is selected (CLKXM = 0 and CLKX is an input), the external falling-edge triggered input clock on CLKX is inverted to a rising-edge triggered clock before being sent to the transmitter. If CLKXP = 1, and internal clocking selected (CLKXM = 1 and CLKX is an output pin), the internal (rising-edge triggered) clock, CLKX\_int, is inverted before being sent out on the CLKX pin.

Similarly, the receiver can reliably sample data that is clocked with a risingedge clock (by the transmitter). The receive clock polarity bit, CLKRP, sets the edge used to sample received data. The receive data is always sampled on the falling edge of CLKR\_int. Therefore, if CLKRP = 1 and external clocking is selected (CLKRM = 0 and CLKR is an input pin), the external rising-edge triggered input clock on CLKR is inverted to a falling-edge clock before being sent to the receiver. If CLKRP = 1 and internal clocking is selected (CLKRM = 1), the internal falling-edge triggered clock is inverted to a rising-edge before being sent out on the CLKR pin.

In a system where the same clock (internal or external) is used to clock the receiver and transmitter, CLKRP = CLKXP. The receiver uses the opposite edge as the transmitter to ensure valid setup and hold times of data around this edge. Figure 8–7 shows how data clocked by an external serial device using a risingedge clock can be sampled by the McBSP receiver with the falling edge of the same clock.

Figure 8–7. Receive Data Clocking

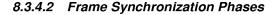

Frame synchronization indicates the beginning of a transfer on the McBSP. The data stream following frame synchronization can have up to two phases, phase 1 and phase 2. The number of phases can be selected by the phase bit, (R/X)PHASE, in the RCR and XCR. The number of elements per frame and bits per element can be independently selected for each phase via (R/X)FRLEN(1/2) and (R/X)WDLEN(1/2), respectively. Figure 8–8 shows a frame in which the first phase consists of two elements of 12 bits each followed by a second phase of three elements of 8 bits each. The entire bit stream in the frame is contiguous; no gaps exist either between elements or phases. Table 8–8 shows the fields in the receive/transmit control registers (RCR/XCR) that control the frame length and element length for each phase for both the receiver and the transmitter. The maximum number of elements per frame is 128 for a single-phase frame and 256 for a dual phase frame. The number of bits per element can be 8, 12, 16, 20, 24, or 32.

Figure 8–8. Dual-Phase Frame Example

Table 8–8. RCR/XCR Fields Controlling Elements per Frame and Bits per Element

| Serial Port |             | RCR/XCR field Control |                  |  |  |  |

|-------------|-------------|-----------------------|------------------|--|--|--|

| McBSP0/1    | Frame Phase | Elements per Frame    | Bits per Element |  |  |  |

| Receive     | 1           | RFRLEN1               | RWDLEN1          |  |  |  |

| Receive     | 2           | RFRLEN2               | RWDLEN2          |  |  |  |

| Transmit    | 1           | XFRLEN1               | XWDLEN1          |  |  |  |

| Transmit    | 2           | XFRLEN2               | XWDLEN2          |  |  |  |

#### 8.3.4.3 Frame Length: (R/X)FRLEN(1/2)

Frame length can be defined as the number of serial elements transferred per frame. The length corresponds to the number of elements or logical time slots or channels per frame synchronization signal. The 7-bit (R/X)FRLEN(1/2) field in the (R/X)CR supports up to 128 elements per frame as shown in Table 8–9. (R/X)PHASE = 0 represents a single-phase data frame and a (R/X)PHASE = 1 selects a dual-phase for the data stream. For a single-phase frame, the value of FRLEN2 does not matter. Program the frame length fields with (*w minus 1*), where *w* represents the number of elements per frame. For Figure 8–8, (R/X)FRLEN1 = 1 or 0000001b and (R/X)FRLEN2 = 2 or 0000010b.

Table 8–9. McBSP Receive/Transmit Frame Length 1/2 Configuration

| (R/X)PHASE | (R/X)FRLEN1       | (R/X)FRLEN2       | Frame Length                                       |

|------------|-------------------|-------------------|----------------------------------------------------|

| 0          | $0 \le n \le 127$ | x                 | Single phase frame; (n+1) words per frame          |

| 1          | $0 \le n \le 127$ | $0 \le m \le 127$ | Dual phase frame; (n+1) plus (m+1) words per frame |

#### 8.3.4.4 Element Length: (R/X)WDLEN(1/2)

The (R/X)WDLEN(1/2) fields in the receive/transmit control register determine the element length in bits per element for the receiver and the transmitter for each phase of the frame, as shown in Table 8–8. Table 8–10 shows how the value of these fields selects particular element lengths in bits. For the example in Figure 8–8, (R/X)WDLEN1 = 001b and (R/X)WDLEN2 = 000b. If (R/X)PHASE = 0, indicating a single-phase frame, (R/X)WDLEN2 is not used by the McBSP and its value does not matter.

| Table 8–10. | McBSP Receive/Transmit element | Length | Configuration |

|-------------|--------------------------------|--------|---------------|

|             |                                |        |               |

| (R/X)WDLEN(1/2) | McBSP Element<br>Length (Bits) |

|-----------------|--------------------------------|

| 000             | 8                              |

| 001             | 12                             |

| 010             | 16                             |

| 011             | 20                             |

| 100             | 24                             |

| 101             | 32                             |

| 110             | Reserved                       |

| 111             | Reserved                       |

|                 |                                |

#### 8.3.4.5 Data Packing using Frame Length and Element Length

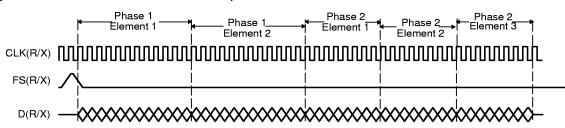

The frame length and element length can be manipulated to effectively pack data. For example, consider a situation in which four 8-bit elements are transferred in a single-phase frame, as shown in Figure 8–9. In this case:

- (R/X)PHASE = 0, indicating a single-phase frame

- □ (R/X)FRLEN1 = 0000011b, indicating a 4-element frame

- $\square$  (R/X)WDLEN1 = 000b, indicating 8-bit elements

In this case, four 8-bit data elements are transferred to and from the McBSP by the CPU or the DMA controller. Four reads of DRR and four writes of DXR are necessary for each frame.

Figure 8–9. Single-Phase Frame of Four 8-Bit Elements

The example in Figure 8–9 can also be viewed as a data stream of a singlephase frame consisting of one 32-bit data element as shown in Figure 8–10. In this case:

$\square$  (R/X)PHASE = 0, indicating a single phase frame

$\square$  (R/X)FRLEN1 = 0b, indicating a 1-element frame

□ (R/X)WDLEN1 = 101b, indicating 32-bit elements

In this case, one 32-bit data element is transferred to and from the McBSP by the CPU or the DMA controller. Thus, one read of DRR and one write of DXR is necessary for each frame. This results in only one-fourth the number of transfers compared to the previous case. This manipulation reduces the percentage of bus time required for serial port data movement.

#### 8.3.4.6 Data Delay: (R/X)DATDLY

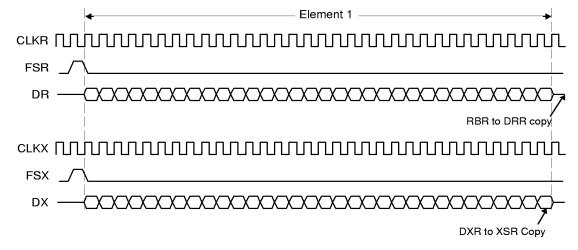

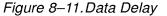

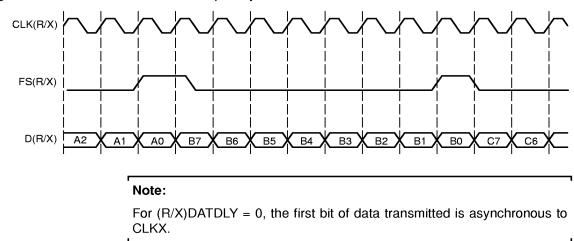

The start of a frame is defined by the first clock cycle in which frame synchronization is found to be active. The beginning of actual data reception or transmission with respect to the start of the frame can be delayed if required. This delay is called data delay. RDATDLY and XDATDLY specify the data delay for reception and transmission, respectively. The range of programmable data delay is zero to two bit-clocks ((R/X)DATDLY = 00b to10b) as described in Table 8–6 and shown in Figure 8–11. Typically 1-bit delay is selected because data often follows a 1-cycle active frame sync pulse.

Normally a frame sync pulse is detected or sampled with respect to an edge of serial clock CLK(R/X). Thus, on a subsequent cycle (depending on data delay value), data can be received or transmitted. However, in the case of zero-bit data delay, the data must be ready for reception and/or transmission on the same serial clock cycle. For reception, this problem is solved by receive data being sampled on the first falling edge of CLKR when an active (high) FSR is detected. However, data transmission must begin on the rising edge of CLKX that generated the frame synchronization. Therefore, the first data bit is assumed to be present in the XSR and DX. The transmitter then asynchronously detects the frame synchronization, FSX goes active, and immediately starts driving the first bit to be transmitted on the DX pin.

Another common operation uses a data delay of 2. This configuration allows the serial port to interface to different types of T1 framing devices in which the data stream is preceded by a framing bit. During reception of such a stream with a data delay of two bits the framing bit appears after a 1-bit delay and data appears after a 2-bit delay), the serial port essentially discards the framing bit from the data stream, as shown in Figure 8–12. In transmission, by delaying the first transfer bit, the serial port essentially inserts a blank period (a high-impedance period) in place of the framing bit. Here, it is expected that the framing device inserts its own framing bit or that the framing bit is generated by another device. Alternatively, you may pull-up or pull-down DX to achieve the desired value.

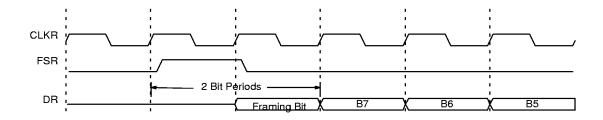

#### 8.3.4.7 Multiphase Frame Example: AC97

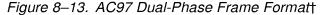

Figure 8–13 shows an example of the Audio Codec '97 (AC97) standard, which uses the dual-phase frame feature. The first phase consists of a single 16-bit element. The second phase consists of 12 20-bit elements. The phases are configured as follows:

- $\square$  (R/X)PHASE = 1b: specifying dual-phase frame

- □ (R/X)FRLEN1 = 0b: specifying 1 element per frame in phase 1

- (R/X)WDLEN1 = 010b: specifying 16-bits per element in phase 1

- $\square$  (R/X)FRLEN2 = 0001011b: specifying 12 elements per frame in phase 2

- (R/X)WDLEN2 = 011b: specifying 20-bits per element in phase 2

- CLK(R/X)P = 0: specifying that the receive data sampled on falling edge of CLKR and transmit data is clocked on rising edge of CLKX

- $\square$  FS(R/X)P = 0: indicating active frame sync signals are used

- $\square$  (R/X)DATDLY = 01b: indicating a data delay of one bit-clock

† PxEy denotes Phase x and Element y

Figure 8–13 shows the AC97 timing near frame synchronization. First the frame sync pulse itself overlaps the first element. In McBSP operation, the inactive-to-active transition of the frame synchronization signal actually indicates frame synchronization. For this reason, frame synchronization can be high an arbitrary number of bit clocks. Only after the frame synchronization is recognized as inactive and then active again is the next frame synchronization recognized.

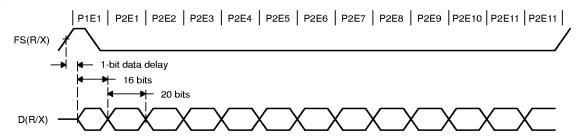

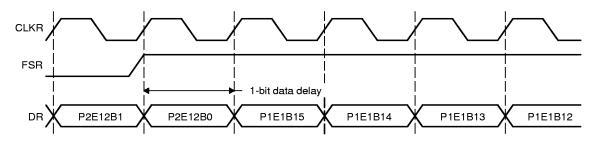

In Figure 8–14, there is 1-bit data delay. Regardless of the data delay, transmission can occur without gaps. The last bit of the previous (last) element in phase 2 is immediately followed by the first data bit of the first element in phase 1 of the next data frame.

Figure 8–14. AC97 Bit Timing Near Frame Synchronizationt

† PxEyBz denotes Phase x, Element y, Bit z

#### 8.3.5 McBSP Standard Operation

During a serial transfer, there are typically periods of serial port inactivity between packets or transfers. The receive and transmit frame synchronization pulse occurs for every serial transfer. When the McBSP is not in the reset state and has been configured for the desired operation, a serial transfer can be initiated by programming (R/X)PHASE = 0 for a single-phase frame with the required number of elements programmed in (R/X)FRLEN1. The number of elements can range from 1 to 128 ((R/X)FRLEN1 = 0x0 to 0x7F). The required serial element length is set in the (R/X)WDLEN1 field in the (R/X)CR. If dual phase is required for the transfer, RPHASE = 1 and each (R/X)FRLEN(1/2) can be set to any value between 0x0 to 0x7F.

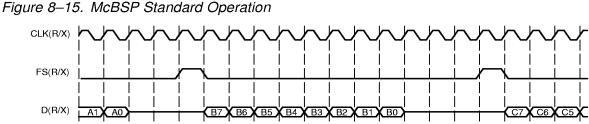

Figure 8–15 shows a single-phase data frame of one 8-bit element. Since the transfer is configured for 1-bit data delay, the data on the DX and DR pins are available one bit clock after FS(R/X) goes active. This figure as well as all others in this section uses the following assumptions:

- $\square$  (R/X)PHASE = 0, specifying a single-phase frame

- (R/X)FRLEN1 = 0b, specifying 1 element per frame

- (R/X)WDLEN1 = 000b, specifying 8-bit element

- $\square (R/X)FRLEN2 = (R/X)WDLEN2 = (value is ignored)$

- $\Box$  CLK(R/X)P = 0, specifying that the receive data is clocked on the falling edge and transmit data is clocked on the rising edge

- $\square$  FS(R/X)P = 0, indicating that active (high) frame sync signals are used

- $\square$  (R/X)DATDLY = 01b, indicating a one-bit data delay

#### 8.3.5.1 Receive Operation

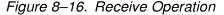

Figure 8–16 shows serial reception. Once the receive frame synchronization signal (FSR) transitions to its active state, it is detected on the first falling edge of the receiver's CLKR. The data on the DR pin is then shifted into the receive shift register (RSR) after the appropriate data delay as set by RDATDLY. The contents of RSR is copied to RBR at the end of every element on the rising edge of the clock, provided RBR is not full with the previous data. Then, an RBR-to-DRR copy activates the RRDY status bit to 1 on the following falling edge of CLKR. This indicates that the receive data register (DRR) is ready with the data to be read by the CPU or the DMA controller. RRDY is deactivated when the DRR is read by the CPU or the DMA controller.

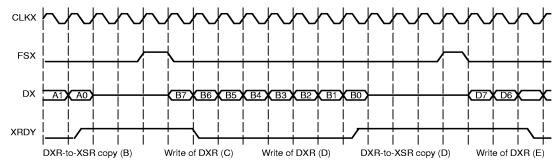

#### 8.3.5.2 Transmit Operation

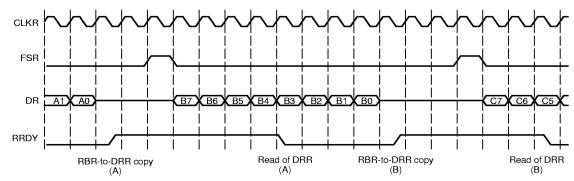

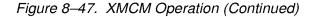

Once transmit frame synchronization occurs, the value in the transmit shift register, XSR, is shifted out and driven on the DX pin after the appropriate data delay as set by XDATDLY. XRDY is activated on every DXR-to-XSR copy on the following falling edge of CLKX, indicating that the data transmit register (DXR) is written with the next data to be transmitted. XRDY is deactivated when the DXR is written by the CPU or the DMA controller. Figure 8-17 illus-

trates serial transmission. See section 8.3.7.4 for transmit operation when the transmitter is pulled out of reset ( $\overline{XRST} = 1$ ).

Figure 8–17. Transmit Operation

#### 8.3.5.3 Maximum Frame Frequency

The frame frequency is determined by the period between frame synchronization signals:

Frame frequency = <u>Bit-clock frequency</u> Number of bit clocks between frame sync signals

The frame frequency may be increased by decreasing the time between frame synchronization signals in bit clocks (limited only by the number of bits per frame). As the frame transmit frequency is increased, the inactivity period between the data frames for adjacent transfers decreases to zero. The minimum time between frame synchronization pulses is the number of bits transferred per frame. This time also defines the maximum frame frequency:

Maximum frame frequency = <u>Bit-clock frequency</u> Number of bits per frame

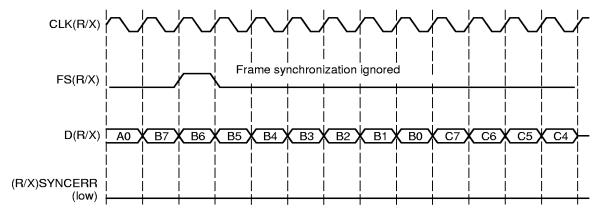

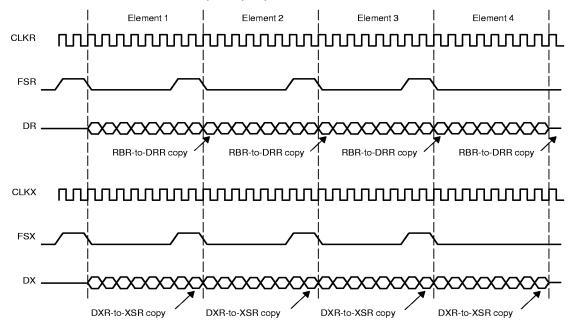

Figure 8–18 shows the McBSP operating at maximum frame frequency. The data bits in consecutive frames are transmitted continuously with no inactivity between bits. If there is a 1-bit data delay, as shown, the frame synchronization pulse overlaps the last bit transmitted in the previous frame.

#### Figure 8–18. Maximum Frame Frequency Transmit and Receive

#### 8.3.6 Frame Synchronization Ignore

The McBSP can be configured to ignore transmit and receive frame synchronization pulses. The (R/X)FIG bit in the (R/X)CR can be set to 0 to recognize frame sync pulses or it can be set to 1 to ignore frame sync pulses. This way, you can use (R/X)FIG to either pack data, if operating at maximum frame frequency, or to ignore unexpected frame sync pulses.

#### 8.3.6.1 Frame Sync Ignore and Unexpected Frame Sync Pulses

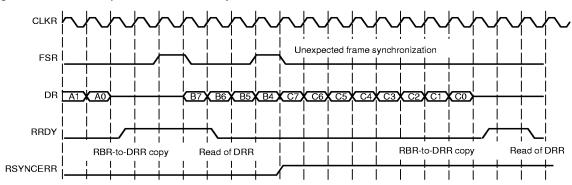

RFIG and XFIG are used to ignore unexpected frame sync pulses. Any frame sync pulse that occurs one or more bit clocks earlier than the programmed data delay from the end of the previous frame specified by ((R/X)DATDLY) is considered unexpected. Setting the frame ignore bits to 1 causes the serial port to ignore these unexpected frame sync signals.

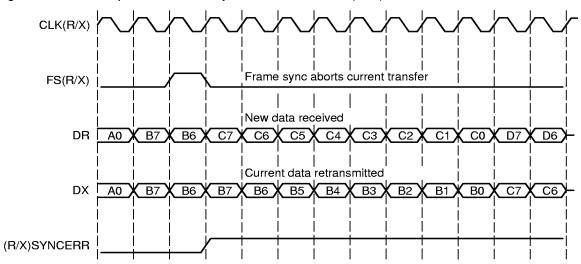

In reception, if not ignored (RFIG = 0), unexpected FSR pulse discards the contents of RSR in favor of the incoming data. Therefore, if RFIG = 0, an unexpected frame synchronization pulse aborts the current data transfer, sets RSYNCERR in the SPCR to 1, and begins the reception of a new data element. When RFIG = 1, the unexpected frame sync pulses are ignored.

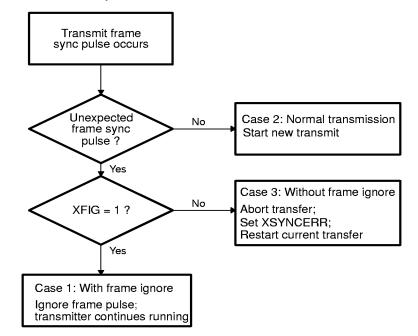

In transmission, if not ignored (XFIG = 0), an unexpected FSX pulse aborts the ongoing transmission, sets the XSYNCERR bit in the SPCR to 1, and re-initiates transmission of the current element that was aborted. When XFIG = 1, unexpected frame sync signals are ignored.

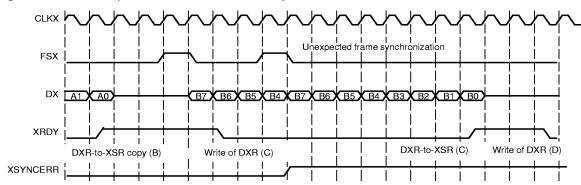

Figure 8–19 shows that element B is interrupted by an unexpected frame sync pulse when (R/X)FIG = 0. The reception of B is aborted (B is lost), and a new data element (C) is received after the appropriate data delay. This condition causes a receive synchronization error and thus sets the RSYNCERR bit. However, for transmission, the transmission of B is aborted, and the same data (B) is re-transmitted after the appropriate data delay. This condition is a transmit synchronization error and thus sets the XSYNCERR bit. Synchronization errors are discussed further in sections 8.3.7.2 and 8.3.7.5.

Figure 8–19. Unexpected Frame Synchronization with (R/X)FIG = 0

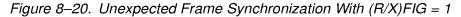

Figure 8–20 shows McBSP operation when unexpected frame synchronization signals are ignored by setting (R/X)FIG = 1. Here, the transfer of element B is not affected by an unexpected frame synchronization.

#### 8.3.6.2 Data Packing using Frame Sync Ignore Bits

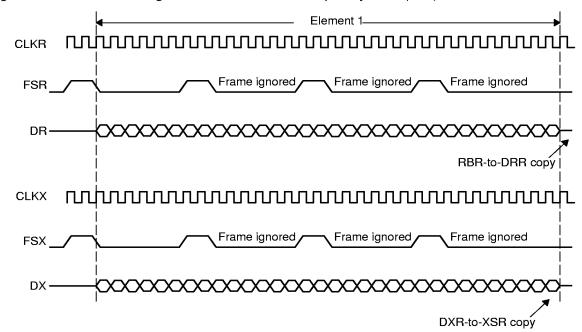

Section 8.3.4.5 describes one method of changing the element length and frame length to simulate 32-bit serial element transfers, thus requiring much less bus bandwidth than four 8-bit transfers require. This example works when there are multiple elements per frame. Now consider the case of the McBSP operating at maximum packet frequency as shown in Figure 8–21. Here, each frame has only a single 8-bit element. This stream takes one read transfer and one write transfer for each 8-bit element. Figure 8–22 shows the McBSP configured to treat this stream as a continuous stream of 32-bit elements. In this example, (R/X)FIG is set to 1 to ignore unexpected subsequent frames. Only one read transfer and one write transfer is needed every 32-bits. This configuration effectively reduces the required bus bandwidth to one-fourth of the bandwidth need to transfer four 8-bit blocks.

Figure 8–21. Maximum Frame Frequency Operation with 8-Bit Data

Figure 8–22. Data Packing at Maximum Frame Frequency With (R/X)FIG = 1

### 8.3.7 Serial Port Exception Conditions

There are five serial port events that can constitute a system error:

- Receive overrun (RFULL = 1)

- Unexpected receive frame synchronization (RSYNCERR = 1)

- Transmit data overwrite

- **Transmit empty** ( $\overline{XEMPTY} = 0$ )

- Unexpected transmit frame synchronization (XSYNCERR = 1)

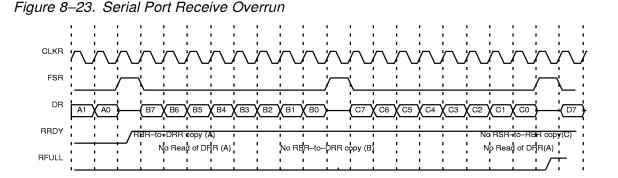

#### 8.3.7.1 Reception With Overrun: RFULL

RFULL = 1 in the SPCR indicates that the receiver has experienced overrun and is in an error condition. RFULL is set when the following conditions are met:

- DRR has not been read since the last RBR-to-DRR transfer.

- RBR is full and an RBR-to-DRR copy has not occurred.

- RSR is full and an RSR-to-RBR transfer has not occurred.

The data arriving on DR is continuously shifted into RSR. Once a complete element is shifted into RSR, an RSR-to-RBR transfer can occur only if an RBR-to-DRR copy is complete. Therefore, if DRR has not been read by the CPU or the DMA controller since the last RBR-to-DRR transfer (RRDY = 1), an RBR-to-DRR copy does not take place until RRDY = 0. This prevents an RSR-to-RBR copy. New data arriving on DR pin is shifted into RSR and the previous contents of RSR is lost. After the receiver starts running from reset, a minimum of three elements must be received before RFULL can be set, because there was no last RBR-to-DRR transfer before the first element.

This data loss can be avoided if DRR is read no later than two and a half CLKR cycles before the end of the third element (data C) in RSR, as shown in Figure 8–23.

Either of the following events clears the RFULL bit to 0 and allows subsequent transfers to be read properly:

- Reading DRR

- $\square$  Resetting the receiver (RRST = 0) or the device.

Another frame synchronization is required to restart the receiver.

Figure 8–23 shows the receive overrun condition. Because element A is not read before the reception of element B is complete, B is not transferred to DRR

yet. Another element, C, arrives and fills RSR. DRR is finally read, but not earlier than two and one half cycles before the end of element C. New data D overwrites the previous element C in RSR. If RFULL is still set after the DRR is read, the next element can overwrite D, if DRR is not read in time.

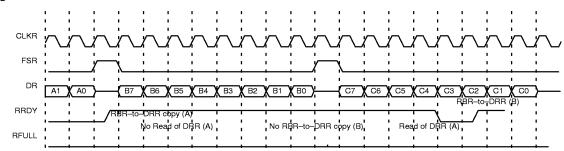

Figure 8–24 shows the case in which RFULL is set but the overrun condition is averted by reading the contents of DRR at least two and a half cycles before the next element, C, is completely shifted into RSR. This ensures that a RBR-to-DRR copy of data B occurs before the next element is transferred from RSR to RBR.

Figure 8–24. Serial Port Receive Overrun Avoided

#### 8.3.7.2 Unexpected Receive Frame Synchronization: RSYNCERR

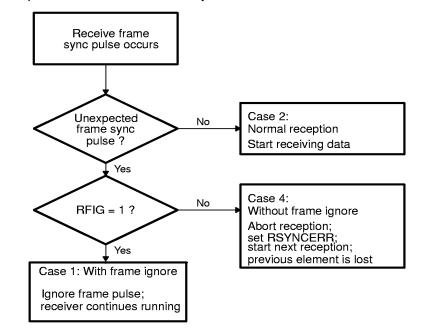

Figure 8–25 shows the decision tree that the receiver uses to handle all incoming frame synchronization pulses. The diagram assumes that the receiver has been activated ( $\overline{RRST} = 1$ ). Unexpected frame sync pulses can originate from an external source or from the internal sample rate generator. An unexpected frame sync pulse is defined as a sync pulse which occurs RDATDLY bit clocks earlier than the last transmitted bit of the previous frame. Any one of four cases can occur:

- Case 1 : Unexpected FSR pulses with RFIG = 1. This case is discussed in section 8.3.6.1 and shown in Figure 8–20. Here, receive frame sync pulses are ignored and the reception continues.

- □ Case 2: Normal serial port reception. There are three reasons for a receive *not* to be in progress:

- This FSR is the first after RRST = 1.

- This FSR is the first after DRR has been read clearing an RFULL condition.

- The serial port is in the inter-packet intervals. The programmed data delay (RDATDLY) for reception may start during these inter-packet intervals for the first bit of the next element to be received. Thus, at maximum frame frequency, frame synchronization can still be received RDATDLY bit clocks before the first bit of the associated element.

For this case, reception continues normally, because these are not unexpected frame sync pulses.

Case 3: Unexpected receive frame synchronization with RFIG = 0 (unexpected frame not ignored). This case was shown in Figure 8–19 for maximum packet frequency. Figure 8–26 shows this case during normal operation of the serial port with time intervals between packets. Unexpected frame sync pulses are detected when they occur the value in RDATDLY bit clocks before the last bit of the previous element is received on DR. In both cases, RSYNCERR in the SPCR is set. RSYNCERR can be cleared only by receiver reset or by writing a 0 to this bit in the SPCR. If RINTM = 11b in the SPCR, RSYNCERR drives the receive interrupt (RINT) to the CPU.

#### Note:

Note that the RSYNCERR bit in the SPCR is a read/write bit, so writing a 1 to it sets the error condition. Typically, writing a 0 is expected.

Figure 8–26. Unexpected Receive Synchronization Pulse

#### 8.3.7.3 Transmit With Data Overwrite

Figure 8–27 depicts what happens if the data in DXR is overwritten before being transmitted. Suppose you load the DXR with data C. A subsequent write to the DXR overwrites C with D before C is copied to the XSR. Thus, C is never transmitted on DX. The CPU can avoid overwriting data by polling XRDY before writing to DXR or by waiting for a programmed XINT to be triggered by XRDY (XINTM = 00b). The DMA controller can avoid overwriting by synchronizing data writes with XEVT.

Figure 8–27. Transmit with Data Overwrite

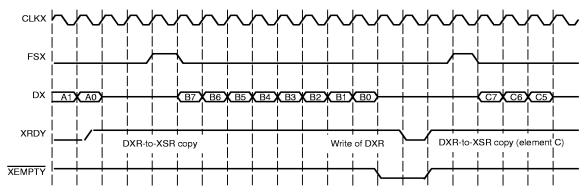

#### 8.3.7.4 Transmit Empty: XEMPTY

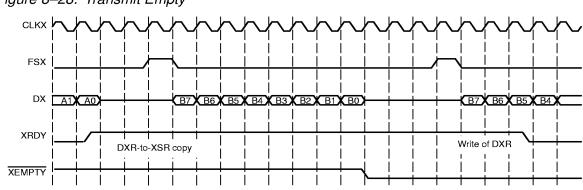

$\overline{XEMPTY}$  indicates whether the transmitter has experienced under-flow. Either of the following conditions causes  $\overline{XEMPTY}$  to become active ( $\overline{XEMPTY} = 0$ ):

- During transmission, DXR has not been loaded since the last DXR-to-XSR copy, and all bits of the data element in the XSR have been shifted out on DX.

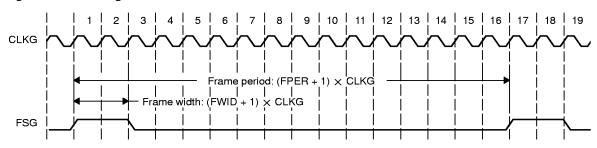

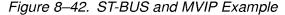

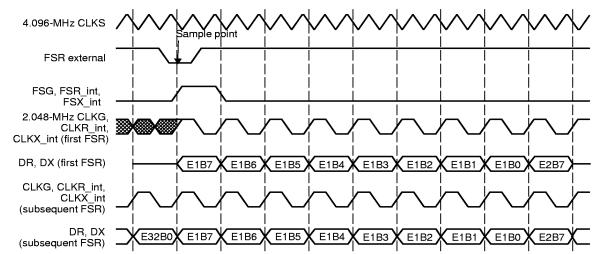

- The transmitter is reset ( $\overline{XRST} = 0$  or device is reset) and then restarted.